į┌ėŗöĄ(sh©┤)¾wųŲųąŻ¼═©│Żė├Ą─╩Ū╩«▀M(j©¼n)ųŲŻ¼╦³ėą0Ż¼1Ż¼2Ż¼3Ż¼ĪŁŻ¼9╩«éĆöĄ(sh©┤)┤aŻ¼ė├╦³éāüĒĮM│╔ę╗éĆöĄ(sh©┤)ĪŻĄ½į┌öĄ(sh©┤)ūųļŖ┬ĘųąŻ¼×ķ┴╦░čļŖ┬ĘĄ─ā╔éĆĀŅæB(t©żi)(1æB(t©żi)║═0æB(t©żi))║═öĄ(sh©┤)┤aī”æ¬(y©®ng)ŲüĒŻ¼▓╔ė├Č■▀M(j©¼n)ųŲ▌^×ķĘĮ▒ŃŻ¼Č■▀M(j©¼n)ųŲų╗ėą0║═1ā╔éĆöĄ(sh©┤)┤aĪŻ

╩«▀M(j©¼n)ųŲ╩Ūęį10×ķĄūöĄ(sh©┤)Ą─ėŗöĄ(sh©┤)¾wųŲŻ¼└²╚ń

Č■▀M(j©¼n)ųŲ╩Ūęį2×ķĄūöĄ(sh©┤)Ą─ėŗöĄ(sh©┤)¾wųŲŻ¼└²╚ń

Č■▀M(j©¼n)ųŲöĄ(sh©┤)11011ŽÓ«ö(d©Īng)ė┌╩«▀M(j©¼n)ųŲöĄ(sh©┤)27ĪŻ

Č■▀M(j©¼n)ųŲ╝ėĘ©Ų„╩ŪöĄ(sh©┤)ūųļŖ┬ĘĄ─╗∙▒Š▓┐╝■ų«ę╗ĪŻČ■▀M(j©¼n)ųŲ╝ėĘ©▀\╦Ń═¼▀ē▌ŗ╝ėĘ©▀\╦ŃĄ─║¼┴x╩Ū▓╗═¼Ą─ĪŻŪ░š▀╩ŪöĄ(sh©┤)Ą─▀\╦ŃŻ¼Č°║¾š▀▒Ē╩Š▀ē▌ŗĻP(gu©Īn)ŽĄĪŻČ■▀M(j©¼n)ųŲ╝ėĘ©╩ŪĪ░ĘĻČ■▀M(j©¼n)ę╗Ī▒Ż¼╝┤1+1=10Ż¼Č°▀ē▌ŗ╝ėät×ķ1+1=1ĪŻ

1Īó░ļ╝ėŲ„

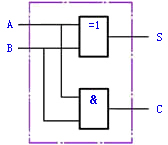

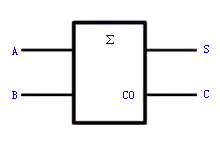

╦∙ų^Ī░░ļ╝ėĪ▒Ż¼Š═╩Ūų╗Ū¾▒Š╬╗Ą─║═Ż¼Ģ║▓╗╣▄Ą═╬╗╦═üĒĄ─▀M(j©¼n)╬╗öĄ(sh©┤)ĪŻ░ļ╝ėŲ„Ą─▀ē▌ŗĀŅæB(t©żi)▒ĒęŖ▒Ē1ĪŻ

|

▒Ē1░ļ╝ėŲ„▀ē▌ŗĀŅæB(t©żi)▒Ē | |||

| A | B | S | C |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

ŲõųąŻ¼A║═B╩ŪŽÓ╝ėĄ─ā╔éĆöĄ(sh©┤)Ż¼S╩Ū░ļ╝ė║═öĄ(sh©┤)Ż¼C╩Ū▀M(j©¼n)╬╗öĄ(sh©┤)ĪŻ

ė╔▀ē▌ŗĀŅæB(t©żi)▒Ē┐╔īæ│÷▀ē▌ŗ╩ĮŻ║

▓óė╔┤╦«ŗ│÷łD1(a)Ą─▀ē▌ŗłDĪŻłD1(b)╩Ū░ļ╝ėŲ„Ą─▀ē▌ŗĘ¹╠¢ĪŻ

|

|

| (a)▀ē▌ŗłD | (b)▀ē▌ŗĘ¹╠¢ |

|

łD1░ļ╝ėŲ„▀ē▌ŗłD╝░Ųõ▀ē▌ŗĘ¹╠¢ | |

2Īó╚½╝ėŲ„

«ö(d©Īng)ČÓ╬╗öĄ(sh©┤)ŽÓ╝ėĢrŻ¼░ļ╝ėŲ„┐╔ė├ė┌ūŅĄ═╬╗Ū¾║═Ż¼▓óĮo│÷▀M(j©¼n)╬╗öĄ(sh©┤)ĪŻĄ┌Č■╬╗Ą─ŽÓ╝ėėąā╔éĆ┤²╝ėöĄ(sh©┤) Ż¼▀Ćėąę╗éĆüĒūįĄ═╬╗╦═üĒĄ─▀M(j©¼n)╬╗öĄ(sh©┤)

Ż¼▀Ćėąę╗éĆüĒūįĄ═╬╗╦═üĒĄ─▀M(j©¼n)╬╗öĄ(sh©┤) ĪŻ▀@╚²éĆöĄ(sh©┤)ŽÓ╝ėŻ¼Ą├│÷▒Š╬╗║═öĄ(sh©┤)(╚½╝ė║═öĄ(sh©┤))

ĪŻ▀@╚²éĆöĄ(sh©┤)ŽÓ╝ėŻ¼Ą├│÷▒Š╬╗║═öĄ(sh©┤)(╚½╝ė║═öĄ(sh©┤)) ║═▀M(j©¼n)╬╗öĄ(sh©┤)

║═▀M(j©¼n)╬╗öĄ(sh©┤) Ż¼▀@Š═╩ŪĪ░╚½╝ėĪ▒Ż¼▒Ē2╩Ū╚½╝ėŲ„Ą─▀ē▌ŗĀŅæB(t©żi)▒Ē

Ż¼▀@Š═╩ŪĪ░╚½╝ėĪ▒Ż¼▒Ē2╩Ū╚½╝ėŲ„Ą─▀ē▌ŗĀŅæB(t©żi)▒Ē

|

▒Ē2╚½╝ėŲ„▀ē▌ŗĀŅæB(t©żi)łD | ||||

|

|

|

|

|

|

0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

0 1 1 0 1 0 0 1 |

0 0 0 1 0 1 1 1 |

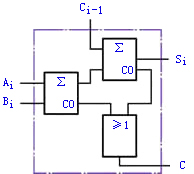

╚½╝ėŲ„┐╔ė├ā╔éĆ░ļ╝ėŲ„║═ę╗éĆ╗“ķTĮM│╔Ż¼╚ńłD2(a)╦∙╩ŠĪŻ į┌Ą┌ę╗éĆ░ļ╝ėŲ„ųąŽÓ╝ėŻ¼Ą├│÷Ą─ĮY(ji©”)╣¹į┘║═

į┌Ą┌ę╗éĆ░ļ╝ėŲ„ųąŽÓ╝ėŻ¼Ą├│÷Ą─ĮY(ji©”)╣¹į┘║═ į┌Ą┌Č■éĆ░ļ╝ėŲ„ųąŽÓ╝ėŻ¼╝┤Ą├│÷╚½╝ė║═

į┌Ą┌Č■éĆ░ļ╝ėŲ„ųąŽÓ╝ėŻ¼╝┤Ą├│÷╚½╝ė║═ ĪŻā╔éĆ░ļ╝ėŲ„Ą─▀M(j©¼n)╬╗öĄ(sh©┤)═©▀^╗“ķT▌ö│÷ū„×ķ▒Š╬╗Ą─▀M(j©¼n)╬╗öĄ(sh©┤)

ĪŻā╔éĆ░ļ╝ėŲ„Ą─▀M(j©¼n)╬╗öĄ(sh©┤)═©▀^╗“ķT▌ö│÷ū„×ķ▒Š╬╗Ą─▀M(j©¼n)╬╗öĄ(sh©┤) ĪŻłD2(b)╩Ū╚½╝ėŲ„Ą─▀ē▌ŗĘ¹╠¢ĪŻ

ĪŻłD2(b)╩Ū╚½╝ėŲ„Ą─▀ē▌ŗĘ¹╠¢ĪŻ

|

|

| (a)▀ē▌ŗłD | (b)▀ē▌ŗĘ¹╠¢ |

|

łD2 ╚½╝ėŲ„▀ē▌ŗłD╝░Ųõ▀ē▌ŗĘ¹╠¢ | |

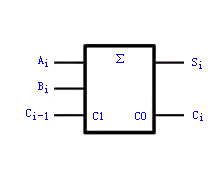

└²1Īóė├4éĆ╚½╝ėŲ„ĮM│╔ę╗éĆ▀ē▌ŗļŖ┬ĘęįīŹ¼F(xi©żn)ā╔éĆ4╬╗Ą─Č■▀M(j©¼n)ųŲöĄ(sh©┤)AĪ¬1101(╩«▀M(j©¼n)ųŲ×ķ13)║═BĪ¬1011(╩«▀M(j©¼n)ųŲ×ķ11)Ą─╝ėĘ©▀\╦ŃĪŻ

ĮŌŻ║

▀ē▌ŗļŖ┬Ę╚ńłD3╦∙╩ŠŻ¼║═öĄ(sh©┤)╩ŪSĪ¬11000(╩«▀M(j©¼n)ųŲöĄ(sh©┤)×ķ24)ĪŻĖ∙ō■(j©┤)╚½╝ėŲ„Ą─▀ē▌ŗĀŅæB(t©żi)▒ĒūįąąĘų╬÷ĪŻ

▀@ĘN╚½╝ėŲ„Ą─╚╬ęŌę╗╬╗Ą─╝ėĘ©▀\╦ŃŻ¼Č╝▒žĒÜĄ╚ĄĮĄ═╬╗╝ėĘ©═Ļ│╔╦═üĒ▀M(j©¼n)╬╗Ģr▓┼─▄▀M(j©¼n)ąąĪŻ▀@ĘN▀M(j©¼n)╬╗ĘĮ╩ĮĘQ×ķ┤«ąą▀M(j©¼n)╬╗Ż¼╦³Ą─╚▒³c╩Ū▀\╦Ń╦┘Č╚┬²Ż¼Ą½ŲõļŖ┬Ę▒╚▌^║åå╬Ż¼ę“┤╦į┌ī”▀\╦Ń╦┘Č╚ę¬Ū¾▓╗Ė▀Ą─įO(sh©©)éõųąŻ¼╚į▓╗╩¦×ķę╗ĘN┐╔╚ĪĄ─╚½╝ėŲ„ĪŻT692╝»│╔╝ėĘ©Ų„Š═╩Ū▀@ĘN┤«ąą╝ėĘ©Ų„ĪŻ

ĘĄ╗žĒö▓┐

ĘĄ╗žĒö▓┐ ╦óą┬Ēō├µ

╦óą┬Ēō├µ Ž┬ĄĮĒōĄū

Ž┬ĄĮĒōĄū